Verilog99题-50-52题

前言

不忘出芯veriloig99题的50-52题是关于亚稳态和复位亚稳态消除问题。

50.解释一下亚稳态。

触发器的建立时间和保持时间在时钟上升沿左右定义了一个时间窗口,如果触发器数据输入端口上的数据在这个时间窗口内发生变化(或者数据更新),那么就会产生时序违规。如果数据在上述窗口中被采集,触发器中的晶体管不能可靠地设置为逻辑0或者逻辑1对应的电平上,导致触发器的输出无法在某个规定时间段内达到一个可以确定的状态,介于0和1之间。亚稳态是可以传播的。

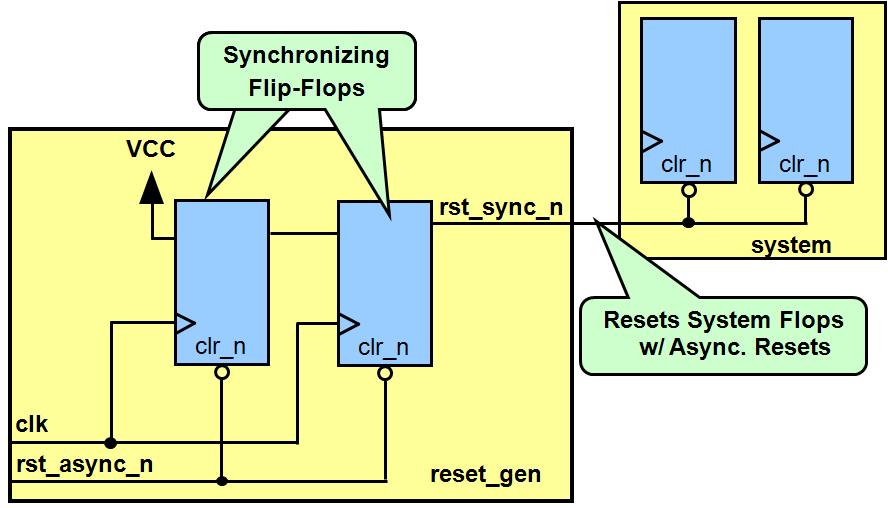

51. 用verilog实现异步复位同步释放电路。

关于异步复位,同步释放的更多内容:FPGA中亚稳态——让你无处可逃

module reset_gen (

input clk ,

input rst_async_n ,

output rst_sync_n

);

reg rst_s1, rst_s2;

always @ (posedge clk or negedge rst_async_n)

if (!rst_async_n)

begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else

begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2; //rst_sync_n才是我们真正对系统输出的复位信号

endmodule

52. 用verilog实现异步复位同步释放电路,支持测试模式的复位信号切换。

module reset_gen (

input clk ,

input rst_async_n ,

input test_shift ,

output rst_sync_n

);

reg rst_s1;

reg rst_s2;

wire tmrst;

assign tmrst = rst_async_n | test_shift;

always @ (posedge clk or negedge tmrst)

if (!tmrst)

begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else

begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2;

endmodule

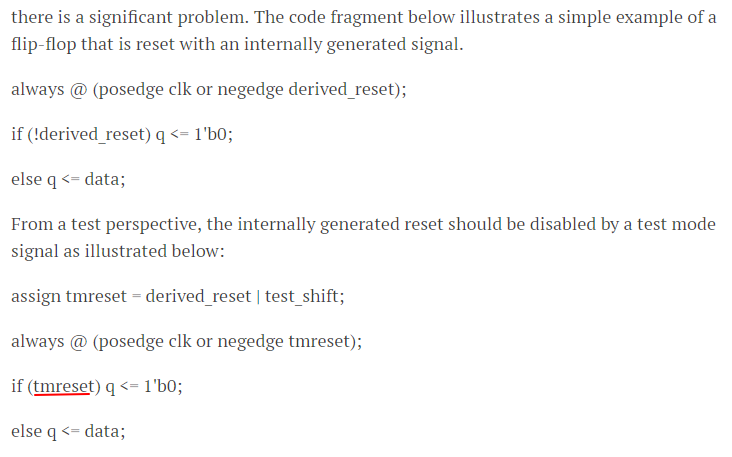

这个测试模式的用意还未领悟,本题的参考链接。以门控时钟和复位信号,讲解了测试模式的一些知识。文章中有一处错误,讲解复位信号的测试模式切换的时候,少写了取反符号(粗心所致)。如下图:

halftop

即将入行的数字IC设计工程师