AMBA-APB总线协议学习

简介

The Advanced Peripheral Bus(APB)is part of the Advanced Microcontroller Bus architecture (AMBA)protocol family. It defines a low-cost interface that is optimized for minimal consumption and reduced interface complexity.

The APB protocol is not pipelined, use it to connect to low-bandwidth peripherals that do not require the high performance of the AXI protocol.

The APB protocol relates a signal transition to the rising edge of the clock, to simplify the integration of APB peripherals into any design flow. Every transfer takes at least two cycles.

The APB can interface with :

AMBA Advanced High-performance Bus (AHB)

AMBA Advanced High-performance Bus Lite (AHB-Lite)

AMBA Advanced Extensible Interface (AXI)

AMBA Advanced Extensible Interface Lite (ax4-Lite)

You can use it to access the programmable control registers of peripheral devices.

版本

- The APB Specification Rev E, released in 1998(过时)

- AMBA 2 APB Specification

- AMBA 3 APB Protocol Specification v1.0

- AMBA APB Protocol Specification v2.0.

信号

英语通俗易懂。

简要翻译一下,建议看上方英文原版。

| 信号名 | 来源 | 说明 |

|---|---|---|

| PCLK | 时钟源 | 系统时钟,传输发生在上升沿 |

| PRESETn | 复位源 | 复位信号,低使能 |

| PADDR | APB桥 | 地址信号,最高可达32位 |

| PPROT | APB桥 | 保护类型,详见手册 |

| PSELx | APB桥 | 片选信号,表示x从机是否被选中 |

| PENABLE | APB桥 | 使能信号,标记传输使能 |

| PWRITE | APB桥 | 读/写控制信号,高位写,低为读 |

| PWDATA | APB桥 | 写数据 |

| PSTRB | APB桥 | 写选通信号,指示哪个字节是有效的数据,详见手册。 |

| PREADY | 从机 | 标记从机是否已将数据发送到总线,高为ready |

| PRDATA | 从机 | 读数据 |

| PSLVERR | 从机 | 故障信号,高为发生故障 |

写时序

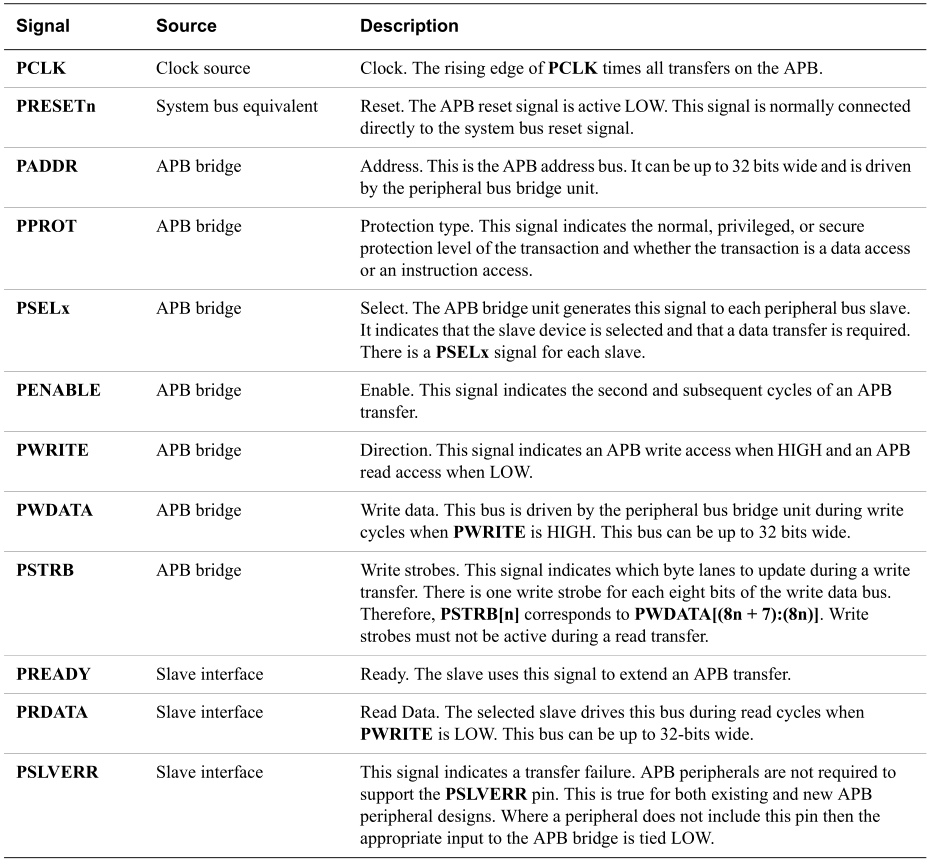

无等待模式

两个阶段:the Setup phase(设置阶段?),the Access phase(访问阶段?)

the Setup phase(设置阶段):在T1,地址PADDR,写入数据PWDATA,写入信号PWRITE和选择信号PSEL在PCLK的上升沿进行寄存,这标志着写操作的开始。

the Access phase(访问阶段):在T2,使能信号PENABLE和就绪信号PREADY在PCLK的上升沿被寄存。

PENABLE变高表示访问阶段的开始;PREADY变高表示从机可以在PCLK的下一个上升沿完成传输。

地址PADDR,写入数据PWDATA和控制信号都要在传输在T3(the Access phase结束)之前保持有效。

使能信号PENABLE在传输结束时被置为低电平。选择信号PSEL也被置为低电平,除非其后紧跟着对同一外设的另一次写操作。

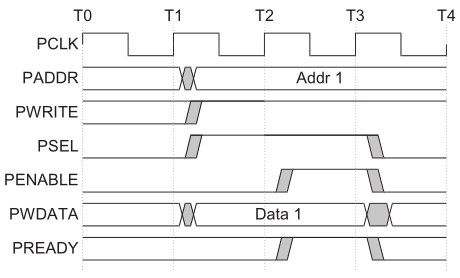

等待模式

等待模式引入从机状态信号PREADY。在访问阶段,当PENABLE为高电平时,从机通过拉低PREADY来延时写操作。PREADY为低电平期间,以下信号保持不变:

- address, PADDR

- write signal, PWRITE

- select signal, PSEL

- enable signal, PENABLE

- write data, PWDATA

- write strobes, PSTRB

- protection type, PPROT.

当PENABLE为低电平时,PREADY可以设置为任何值以确保具有固定双周期访问权限的外设可以将PREADY置为高电平。

注意:推荐直到下一次访问开始,地址和写操作相关信号一直保持不变。这样可以降低功耗。

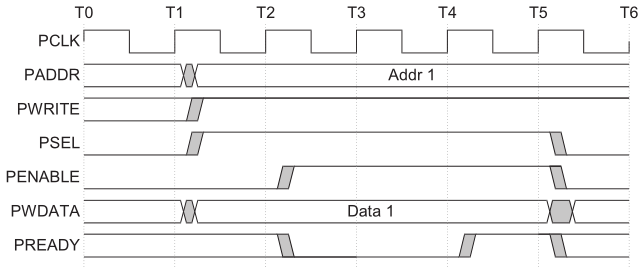

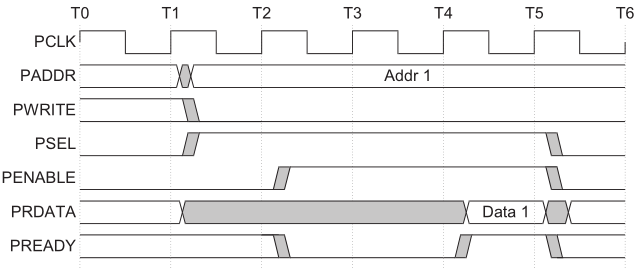

读时序

无等待模式

对照无等待写时序理解,从器件必须在读传输结束前提供数据。

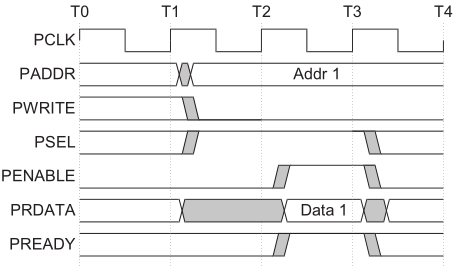

等待模式

如果在访问阶段PREADY被从机置为低电平,则传输会延时。PREADY为低电平期间,以下信号保持不变:

- address, PADDR

- write signal, PWRITE

- select signal, PSEL

- enable signal, PENABLE

- protection type, PPROT.

下图显示延时两个时钟周期:

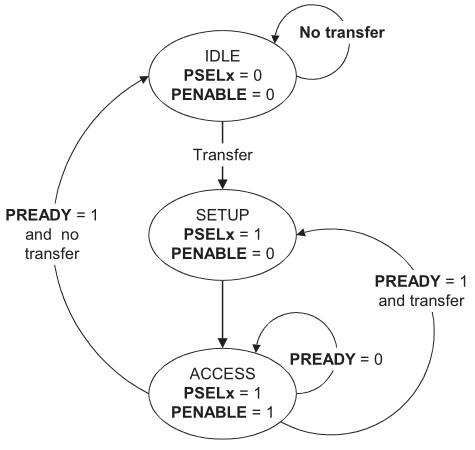

系统状态转移

-

IDLE:初始状态,也是等待传输状态。当片选信号PSELx拉高时总线请求通信,进入SETUP状态

-

SETUP:设置阶段,主从机在该状态设置相应的信号,准备好所有数据。只在该状态停留一个周期,总是在时钟的下一个上升沿到来时进入ACCESS阶段。

-

ACCESS:访问阶段,拉高PENABLE信号。在从SETUP到ACCESS状态的转换期间,地址,写入,选择和写入数据信号必须保持稳定。

退出ACCESS阶段由从机状态信号PREADY控制:

- 当PREADY信号拉高,传输完成,根据是否有下一次传输(PSELx是否为高),进入IDLE状还是SETUP状态。

- 当PREADY信号为低,数据未准备好,在ACCESS状态等待PREADY信号拉高。

其它功能(日后补充)

写选通

传输错误响应

保护单元支持

即将入行的数字IC设计工程师