Verilog99题-57题(单脉冲信号的跨时钟域传输)

题目

在clk a时钟域的一个单周期脉冲信号,如何正确的传递到clk b时钟域? 要考虑clk a和b的各种不同频率/相位的场景。

总结

关于单bit信号的跨时钟域传输这篇博客总结的比较详细,这里直接copy一下结论:

- 在跨时钟域的时候,不一定需要跨时钟域电路(同步器或者握手信号),接近异步时钟或者就是异步时钟的时候跨时钟域就得加上了。

- 在慢到快的时钟域中,加上触发器链(两级触发器)基本上就可以了,主要是抑制亚稳态的传播。

- 但是在快到慢的时钟域中,不仅需要触发器链进行抑制亚稳态的传播,还要防止慢时钟域采不到快时钟域的数据,因此就添加反馈/握手电路(这个反馈信号是指跨时钟域的反馈信号)。(可以使用脉冲展宽)

Verilog描述

参考了NingHeChua*的描述

慢时钟域到快时钟域,两级寄存器同步

module Sync_Pulse(

input clkb,

input rst_n,

input pulse_ina,

output pulse_outb

);

reg signal_r;

reg signal_rr;

always @ (posedge clkb or negedge rst_n)

if (!rst_n) begin

signal_r <= 1'b0;

signal_rr <= 1'b0;

end else begin

signal_r <= pulse_ina;

signal_rr <= signal_r;

end

assign pulse_outb = signal_rr;

endmodule

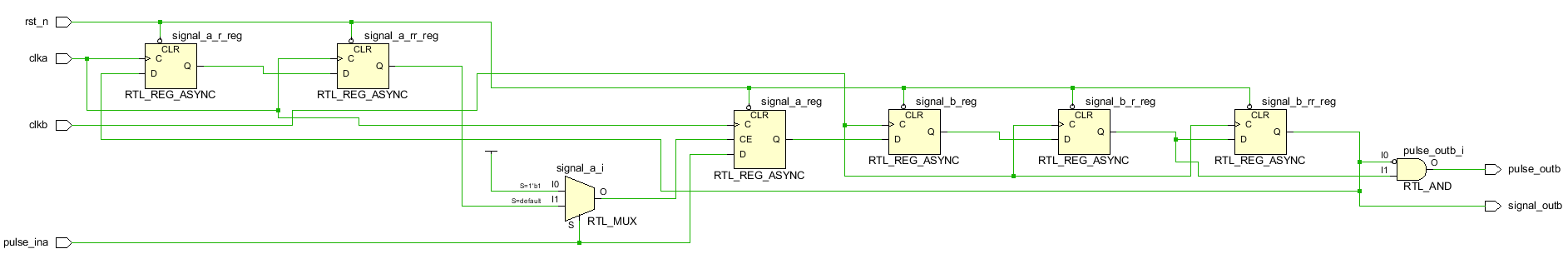

快时钟域到慢时钟域

module Sync_Pulse(

input clka,

input clkb,

input rst_n,

input pulse_ina,

output pulse_outb,

output signal_outb

);

//-------------------------------------------------------

reg signal_a;

reg signal_b;

reg signal_b_r;

reg signal_b_rr;

reg signal_a_r;

reg signal_a_rr;

//-------------------------------------------------------

//在clka下,生成展宽信号signal_a

always @(posedge clka or negedge rst_n)begin

if(rst_n == 1'b0)begin

signal_a <= 1'b0;

end

else if(pulse_ina == 1'b1)begin

signal_a <= 1'b1;

end

else if(signal_a_rr == 1'b1)

signal_a <= 1'b0;

else

signal_a <= signal_a;

end

//-------------------------------------------------------

//在clkb下同步signal_a

always @(posedge clkb or negedge rst_n)begin

if(rst_n == 1'b0)begin

signal_b <= 1'b0;

end

else begin

signal_b <= signal_a;

end

end

//-------------------------------------------------------

//在clkb下生成脉冲信号和输出信号

always @(posedge clkb or negedge rst_n)begin

if(rst_n == 1'b0)begin

signal_b_r <= 'b0;

signal_b_rr <= 'b0;

end

else begin

signal_b_rr <= signal_b_r;

signal_b_r <= signal_b;

end

end

assign pulse_outb = ~signal_b_rr & signal_b_r;

assign signal_outb = signal_b_rr;

//-------------------------------------------------------

//在clka下采集signal_b_rr,生成signal_a_rr用于反馈拉低signal_a

always @(posedge clka or negedge rst_n)begin

if(rst_n == 1'b0)begin

signal_a_r <= 'b0;

signal_a_rr <= 'b0;

end

else begin

signal_a_rr <= signal_a_r;

signal_a_r <= signal_b_rr;

end

end

endmodule

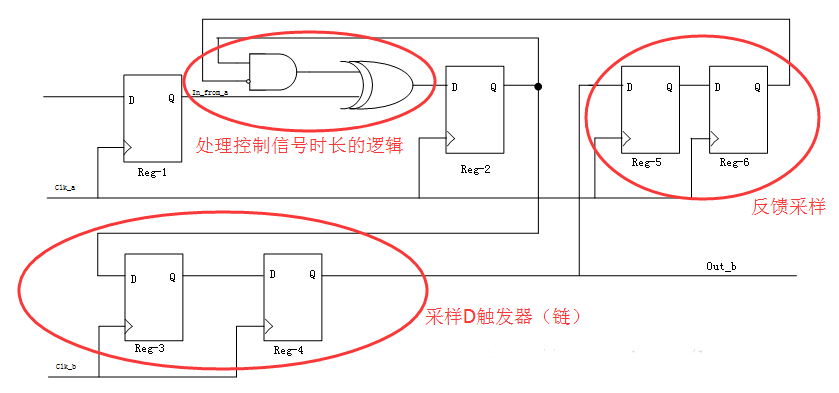

补充一张采用与门、或门、非门、异或门、触发器实现的跨时钟域单bit信号传输的电路图,某发科2020年提前批招聘笔试就要求画出这张图。

图中的“处理控制信号时长的逻辑”与本文中的“脉冲展宽”是同一概念。

本图转载自这篇博客。

halftop

即将入行的数字IC设计工程师