Verilog99题——43、44题(两道算法题)

题目

- 用verilog实现

y(n) = x(n) + x(n-1) + x(n-2) + x(n-3) + x(n-4)+ x(n-5)+ x(n-6)+ x(n-7)输入x是8bit无符号数。- 用verilog实现

y(n) = 0.75*x(n) + 0.25*y(n-1)x, y是8bit无符号数。

43

用移位寄存器实现时延,这里参数化了位宽和个数,注意组合逻辑中阻塞赋值的用法。

verilog描述

// --------------------------------------------------------------------

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// --------------------------------------------------------------------

// Author: halftop

// Github: https://github.com/halftop

// Email: yu.zh@live.com

// Description: y(n) = x(n) + x(n-1) + x(n-2) + x(n-3) + x(n-4)+ x(n-5)+ x(n-6)+ x(n-7)+···

// Dependencies:

// LastEditors: halftop

// Since: 2019-05-09 10:30:00

// LastEditTime: 2019-05-09 15:58:20

// ********************************************************************

// Module Function:

`timescale 1ns / 1ps

module test43

#(

parameter WIDTH = 8 ,

DEPTH = 8 ,

YWD = WIDTH+clogb2(DEPTH)

)

(

input clk ,

input rst_n ,

input [WIDTH-1:0] i_data ,

output reg [YWD-1:0] o_y

);

reg [WIDTH-1:0] data_r [DEPTH-1:0];

integer i;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

for ( i=0 ;i<DEPTH ;i=i+1 ) begin

data_r[i] <= 'd0;

end

end else begin

data_r[0] <= i_data;

for ( i=1 ;i<DEPTH ;i=i+1 ) begin

data_r[i] <= data_r[i-1];

end

end

end

reg [YWD-1:0] sum_comb;

always @(*) begin

sum_comb = 'd0;

for ( i=0 ;i<DEPTH ; i=i+1) begin

sum_comb = sum_comb + data_r[i];

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

o_y <= 'd0;

end else begin

o_y <= sum_comb;

end

end

function integer clogb2 (input integer depth);

begin

for(clogb2=0; depth>1; clogb2=clogb2+1)

depth = depth >> 1;

end

endfunction

endmodule

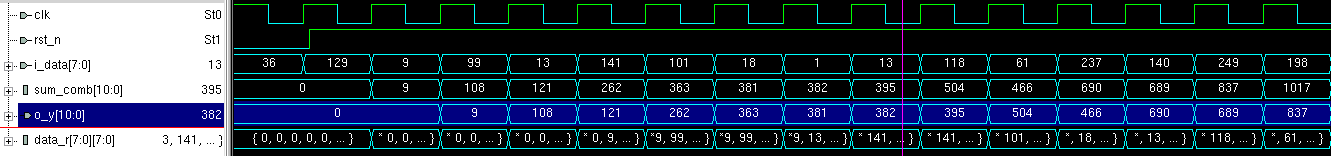

仿真图

注意其中非阻塞式赋值起到的关键作用。

verilog描述

module test44(

input clk ,

input rst_n ,

input [7:0] i_data ,

output [7:0] o_y

);

// y(n) = 0.75x(n) + 0.25y(n-1)

//0.75*4 = 3,0.25*4 = 1

reg [9:0] dout;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

dout <= 'd0;

end else begin

dout <= 3*i_data + dout;

end

end

assign o_y = dout>>2;

endmodule

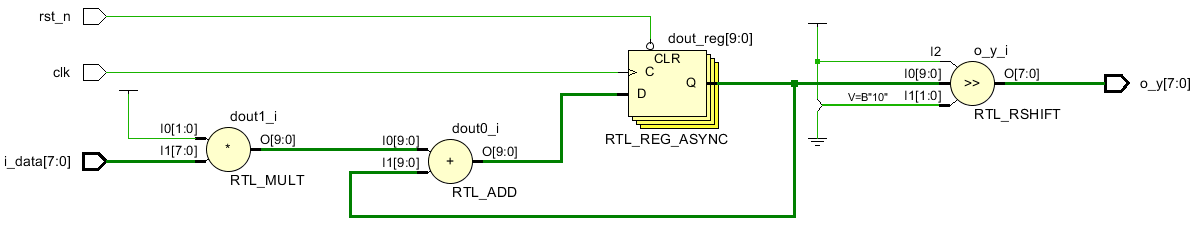

综合出的电路图

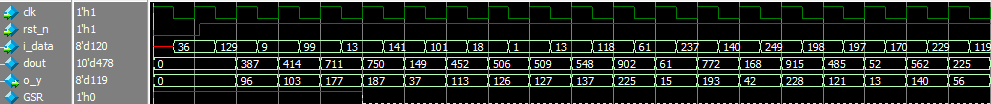

仿真结果

halftop

即将入行的数字IC设计工程师