Verilog99题——45.46题(奇、偶分频)

题目

- 用verilog实现二分频。

- 用verilog实现三分频电路,要求输出50%占空比。

思路及方法

偶数分频十分简单,只需用高速时钟做一个同步计数器,然后在相应的位抽头即可。奇数分频电路相对复杂些。引用一篇比较详细的blog:verilog实现简单分频器

45

verilog描述

// --------------------------------------------------------------------

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// --------------------------------------------------------------------

// Author: halftop

// Github: https://github.com/halftop

// Email: yu.zh@live.com

// Description: 二分频

// Dependencies:

// LastEditors: halftop

// Since: 2019-05-10 10:37:19

// LastEditTime: 2019-05-10 11:04:06

// ********************************************************************

// Module Function:二分频

`timescale 1ns / 1ps

module div_2(

input clk ,

input rst_n ,

output reg clk_out

);

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

clk_out <= 1'b0;

end else begin

clk_out <= ~clk_out;

end

end

endmodule

46

verilog描述

// --------------------------------------------------------------------

// >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<<

// --------------------------------------------------------------------

// Author: halftop

// Github: https://github.com/halftop

// Email: yu.zh@live.com

// Description: 实现任意奇数分频

// Dependencies:

// LastEditors: halftop

// Since: 2019-05-10 11:04:51

// LastEditTime: 2019-05-10 22:18:17

// ********************************************************************

// Module Function:实现任意奇数分频

`timescale 1ns / 1ps

module div_odd

#(

parameter N = 3

)

(

input clk ,

input rst_n ,

output clk_out

);

localparam WD = clogb2(N);

reg clk_out_p ;

reg clk_out_n ;

reg [WD-1:0] count ;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

count <= 'd0;

end else if (count==N-1) begin

count <= 'd0;

end else begin

count <= count + 1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

clk_out_p <= 1'b1;

end else if (count>N/2) begin

clk_out_p <= 1'b0;

end else begin

clk_out_p <= 1'b1;

end

end

always @(negedge clk or negedge rst_n) begin

if (!rst_n) begin

clk_out_n <= 1'b0;

end else begin

clk_out_n <= clk_out_p;

end

end

assign clk_out = clk_out_p&clk_out_n;

function integer clogb2 (input integer depth);

begin

for(clogb2=0; depth>0; clogb2=clogb2+1)

depth = depth >> 1;

end

endfunction

endmodule

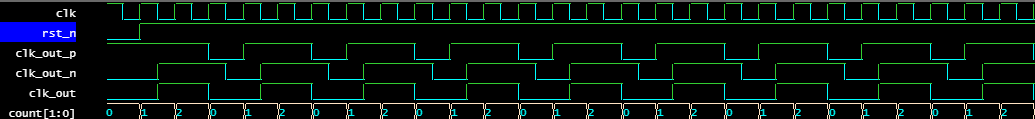

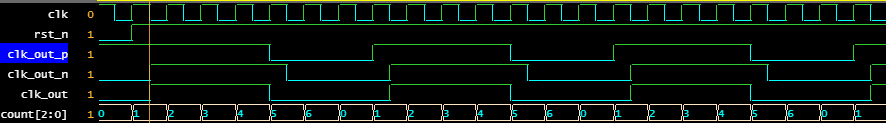

仿真结果

三分频:

七分频:

halftop

即将入行的数字IC设计工程师