通过做verilog99题的第11题学习竞争与冒险

题目

011.什么是竞争和冒险?

注:以下都是知识的搬运和总结,参考文献在最后。

冒险现象

在信号传输与状态变换时会发生的延迟(Delay)。事实上,由于这些延迟,当输入信号发生变化时,其输出信号不能立即跟随输入信号的变化而变化,而是经过一段过渡时间后才能达到原先所期望的状态,从而可能产生瞬间的错误输出,造成逻辑功能的瞬时紊乱。这种现象被称为逻辑电路的“冒险现象”(Hazard),简称“险象”。

产生冒险的原因——竞争

在组合逻辑电路中,输入信号的变化传输到电路各级门时,在时间上有先有后,这种先后所形成的时间差称为竞争(Competition)。

-

分类一:逻辑竞争和功能竞争

-

逻辑竞争:某一个输入端到达某个输出端存在多条不同延迟的信号途径,导致的竞争为逻辑竞争(Logic competition)。

-

功能竞争:如果多个输入端同时存在到达某个输出端的不同延迟的信号途径,则称为功能竞争(Function competition)。

-

-

分类二:非临界竞争和临界竞争——竞争不一定带来错误的输出。

-

非临界竞争:把不会使电路产生错误输出的竞争称为非临界竞争(Non-critical competition)。

-

临界竞争:而把产生错误输出的竞争称为临界竞争(Critical competition)。临界竞争产生的错误输出是在输出波形上出现不需要的尖峰脉冲(毛刺)(Glitch),暂时地破坏正常的逻辑关系。一旦瞬态过程结束,即可恢复正常的逻辑关系。

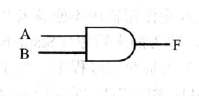

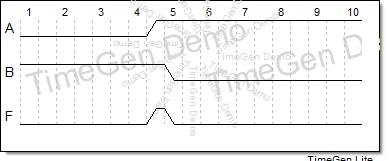

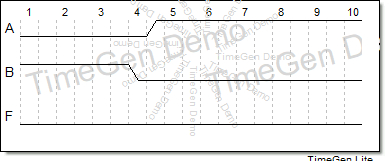

如下图中,因为F=AB,当AB取值为01或10时,F的值应该恒等于0,然而如中间图所示在AB由01变为10的过程中,由于A先于B变化而产生了正向干扰脉冲,这种由于输入信号的到达时间不同而产生的干扰属于功能竞争,这种竞争属于临界竞争。若右图所示,B先于A变化为低电平,即使A信号再变为高电平,在输出端也不会产生干扰脉冲。这种竞争称为非临界竞争。

-

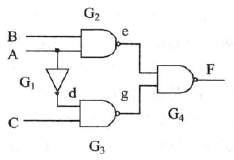

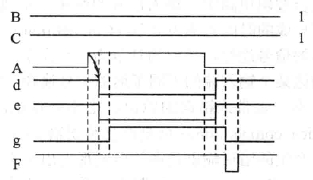

当B=C=1时,F应该恒等于1,这是在理想条件下得出得结论。实际上,门电路都存在延迟时间,假设每个门电路的延迟时间都为t。

当A由低电平变为高电平,经过门延迟t后,反相器G1的输出d由高电平变为低电平,同时与非门G2的输出e也由高电平变为低电平,在G1的输出d为低电平之前,d仍然维持高电平不变,因此G3的输出g不变;再经过门延迟t后,与非门G3的输出g由低变为高电平。由于之前e已经为低电平,以输出F恒定为高电平不变。没有出现尖脉冲,即没有出现险象,所以该竞争是逻辑竞争、非临界竞争。

而A由高电平变为低电平时,经过门延迟t后,反相器G1的输出d由低电平变为高电平,同时与非门G2的输出e也由低电平变为高电平;再经过门延t后,与非门G3的输出g才由高电平变为低电平。由图可以看出,在t的持续时间内,与非门Ga的输入都为高电平,再经过t后,输出持续时间为t低电平尖脉冲,也就是说,这次竞争产生了险象,是逻辑临界竞争。

冒险的判断方法

- 代数法

- 卡诺图法

当某个变量A同时以原变量和反变量的形式出现在逻辑函数表达式中,且在一定条件下该逻辑函数表达式可以简化为A+A'或AA'的形式时,则该逻辑函数表达式对应的电路在变量A发生变化时,可能由于竞争而产生险象。

在代数法的判断中,首先检查函数表达式中是否存在具备竞争条件的变量,即是否同时存在某个变量的原变量和反变量。若存在,则将其他变量的所有取值组合依次代入逻辑函数表达式中,看逻辑函数是否能成为A+A'或A·A'的形式,若能,则在此条件下,逻辑电路可能产生险象;否则,在该种变量的取值组合情况,逻辑电路不会产生险象。

在卡诺图判断方法中,首先做出逻辑函数的卡诺图,并画出与逻辑函数表达式中各“与”项(“或”项)完全对应的圈。然后观察卡诺图,若有圈“相切”,即两圈之间存在不被同一圈包含的相邻最小项,则该电路可能产生险象。“切点”的变量取值即为可能发生险象的固定变量取值。

冒险的消除方法

- 通过增加选通电路:增加选通电路一方面需要增加电路成本,另一方面需要预测险象出现的时刻以便消除,实现比较困难。

- 接入高频滤波电容:因为竞争-冒险所产生的干扰脉冲一般很窄,所以可以采用在输出端连接一个小电容到地的方法,消除干扰脉冲。干扰脉冲的持续时间与门电路的传输延迟属同一数量级,在TTL电路中,只需要几百皮法的电容,就足以把干扰脉冲削弱到开门电平以下。

- 改变逻辑设计并增加冗余项:当冒险是由单个变量改变状态而引起时,可以通过在“切点”增加冗余项的方法予以消除。

FPGA器件的竞争与冒险的消除方法

注:只做总结,详见后两篇参考文献。

- 在系统中尽可能采用同步电路:D触发器的D输入端对毛刺不敏感。

- 在输出信号的保持时间内对其进行“采样”。

- 采样信号

- 将组合电路和时序电路结合起来变成同步时序电路。

- 使用格雷码。格雷码在转化时只有一个输出信号改变,从而不会引起竞争冒险现象。

参考文献

即将入行的数字IC设计工程师