Verilog没有葵花宝典——day3(标准单元库)

题目

- 了解目录结构:与前端相关的比如文档(doc),仿真模型(verilog/vhdl),标准单元库(synopsys/symbols)。

- 阅读文档transition time, propagation delay等参数的定义。

- 阅读文档Power Dissipation/Calculation的描述。

- 阅读文档Delay calculation的描述。

- 提供了哪些类型的cell?

- Verilog文件中包含了哪些信息?

今天的答案基本靠抄(流下了没有知识的眼泪)。

2. 阅读文档transition time, propagation delay等参数的定义。

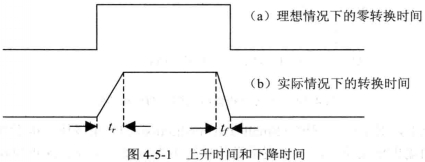

transition time(转化时间):信号从10% Vdd变化到90% Vdd的时间,包括上升时间和下降时间。

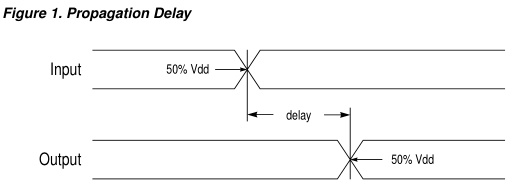

propagation delay(传播延时):输入信号变化到超过50%Vdd与输出信号变化到超过50%Vdd的时间间隔。

3. 阅读文档Power Dissipation/Calculation的描述。

Power Dissipation(功耗,功率损耗)取决于电源电压、工作频率、内部电容和输出负载,并提供计算公式:

Pavg=n=1∑x(Ein∙fin)+n=1∑y(Con∙Vdd2∙21fon)+Eos∙fo1

参数定义见其文档Power Calculation一节。

4. 阅读文档Delay calculation的描述。

总传播延时的估算公式

tTPD=(KProcess)⋅[1+(KVolt⋅ΔVdd)]⋅[1+(KTemp⋅ΔT)]⋅ttypical

参数定义见其文档Delay Calculation一节。

5. 提供了哪些类型的cell?

Special Cells:Antenna-Fix Cell、NWELL and Substrate Tie Cell、Fill Cells、Low-Power (XL) Cells、TIEHI/LO Cells、Delay Cells。

Base Cells:全加器、与门、与或门、BUF、D触发器、延迟、反相器、选择器、与非门、或非门、三态门、异或门、同或门等等。

6. Verilog文件中包含了哪些信息?

粗略地看了一下

有cell的输入、输出端口定义,延迟参数和路径延迟信息以及时序参数(比如说建立时间、保持时间)信息。这些应该都能和文档里的参数对应上。

halftop

即将入行的数字IC设计工程师