Verilog没有葵花宝典——day1(进制与编码)

题目

- bit, byte, word, dword, qword的区别。

- 什么是原码,反码,补码,符号-数值码。以8bit为例,给出各自表示的数值范围。

- 十进制转换为二进制编码: 127, (-127),127.375,(-127.375)

- 设计BCD译码器,输入0~9。采用verilog描述并画出门级电路图。

- 异步FIFO深度为17,如何设计地址格雷码?

第一题

bit:位,二进制中的一位,是计算机存储信息的最小单位;

byte:字节,1byte=8bit;

word:字,1word=2byte=16bit;

dword:双字,double word,1dword=2word=4byte=32bit;

qword:四字,quad-word,1qword=4word=8byte=64bit。

第二题

这个题目以前做过,这里再复习一遍。

原码:带符号数的符号数值码表示,又称作原码,用二进制数位串的最高有效位(MSB)作为符号位,0表示正号(Plus),1表示负号(Minus),其余较低位表示数的绝对值(数值)(Magnitude)。以8bit为例,最大——0111_1111;最小——1111_1111,范围-127~+127。

反码:正数的反码是它本身,负数的反码是保留符号位,其它位按位取反。范围与原码相同,以8bit为例是-127~+127。

补码:正数的补码是它本身,负数的补码是保留符号位,其它位按位取反再加1。以4bit为例,表示范围为-128~+127。

符号-数值码:sign magnitude,有的教材认为与原码一样;有的教材认为符号-数值码相较于原码没有负0。范围-127~+127。

第三题

仍然是复习。

整数部分最基础的就是“除2取余法”,小数部分是"乘2取整法"。

整数部分比较快捷的方法:127=64+32+16+8+4+2+1=26+25+24+23+22+21+20=(1111111)b。

小数部分没有什么比较快的,就是基础法:0.375×2=0.75取0;0.75×2=1.5取1;0.5×2=1取1。

所以可得

127 → 0111_1111

-127 → 1111_1111

127.375 → 0111_1111.011

-127.375 → 1111_1111.011

第四题

verilog描述

module BCD_Decoder(

input [3:0] A,

//output reg [9:0] Y_L

output [9:0] Y_L

);

always @ (*)

case(A)

4'd0:Y_L=10'b11_1111_1110;

4'd1:Y_L=10'b11_1111_1101;

4'd2:Y_L=10'b11_1111_1011;

4'd3:Y_L=10'b11_1111_0111;

4'd4:Y_L=10'b11_1110_1111;

4'd5:Y_L=10'b11_1101_1111;

4'd6:Y_L=10'b11_1011_1111;

4'd7:Y_L=10'b11_0111_1111;

4'd8:Y_L=10'b10_1111_1111;

4'd9:Y_L=10'b01_1111_1111;

default:Y_L=10'b11_1111_1111;

endcase

/*

assign Y_L[0] = ~(~A[3] & ~A[2] & ~A[1] & ~A[0]);

assign Y_L[1] = ~(~A[3] & ~A[2] & ~A[1] & A[0]);

assign Y_L[2] = ~(~A[3] & ~A[2] & A[1] & ~A[0]);

assign Y_L[3] = ~(~A[3] & ~A[2] & A[1] & A[0]);

assign Y_L[4] = ~(~A[3] & A[2] & ~A[1] & ~A[0]);

assign Y_L[5] = ~(~A[3] & A[2] & ~A[1] & A[0]);

assign Y_L[6] = ~(~A[3] & A[2] & A[1] & ~A[0]);

assign Y_L[7] = ~(~A[3] & A[2] & A[1] & A[0]);

assign Y_L[8] = ~(A[3] & ~A[2] & ~A[1] & ~A[0]);

assign Y_L[9] = ~(A[3] & ~A[2] & ~A[1] & A[0]);

*/

endmodule

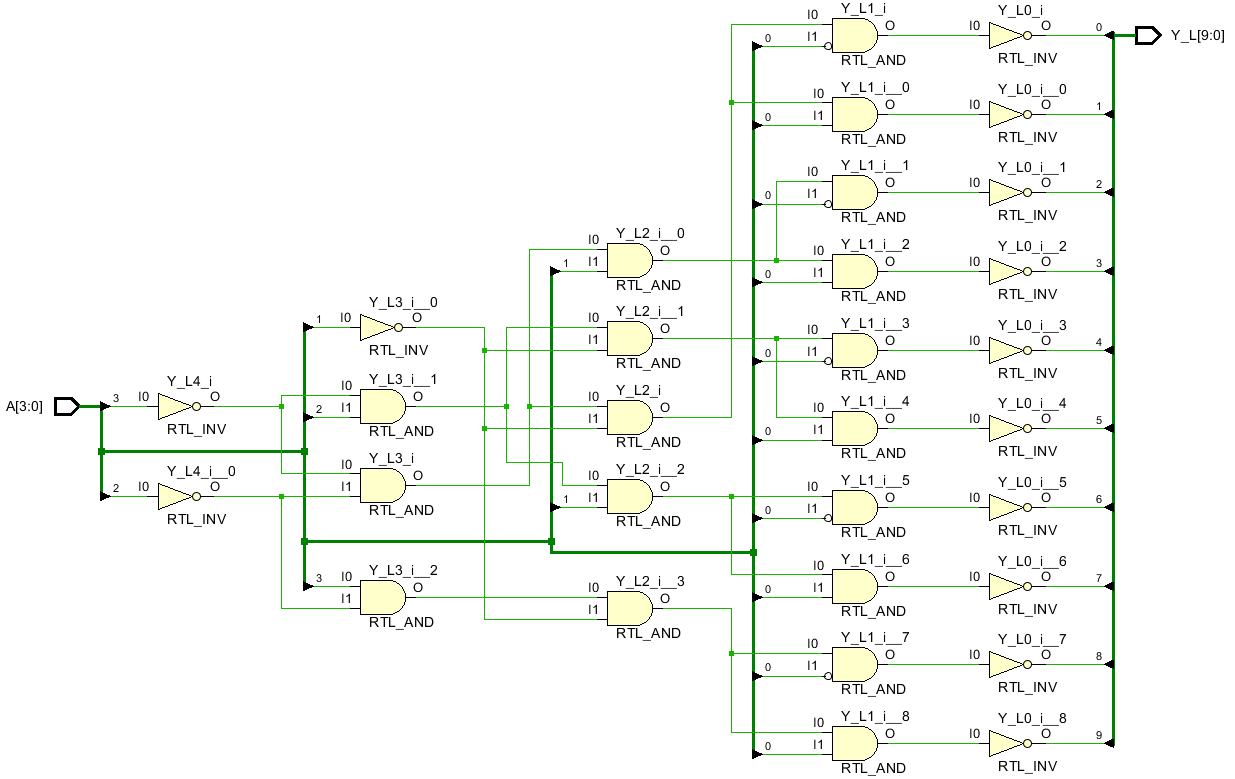

思路及电路图

第五题(待后续研究)

只能偶数,深度为18(5bit)

00100 →

01100 →

01101 →

01111 →

01110 →

01010 →

01011 →

01001 →

01000 →

11000 →

11001 →

11011 →

11010 →

11110 →

11111 →

11101 →

11100 →

10100 →

也有文档说17+17的(6bit)

001000 →

011000 →

011001 →

011011 →

011010 →

011110 →

011111 →

011101 →

011100 →

010100 →

010101 →

010111 →

010110 →

010010 →

010011 →

010001 →

010000 →

110000 →

110001 →

110011 →

110010 →

110110 →

110111 →

110101 →

110100 →

111100 →

111101 →

111111 →

111110 →

111010 →

111011 →

111001 →

111000 →

101000 →

即将入行的数字IC设计工程师