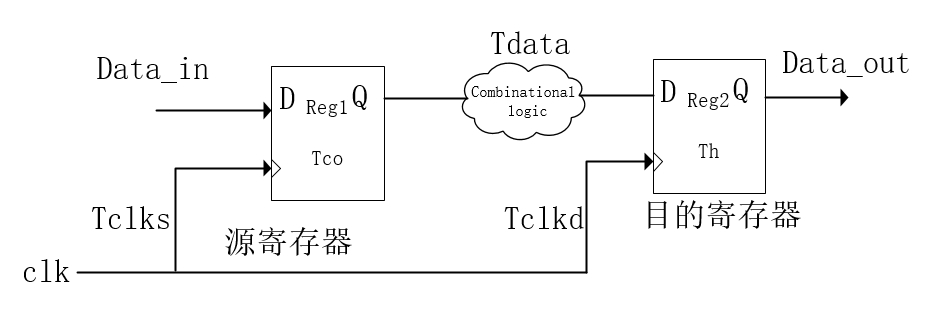

数字电路时序初步及最小时钟周期计算

几个时间概念

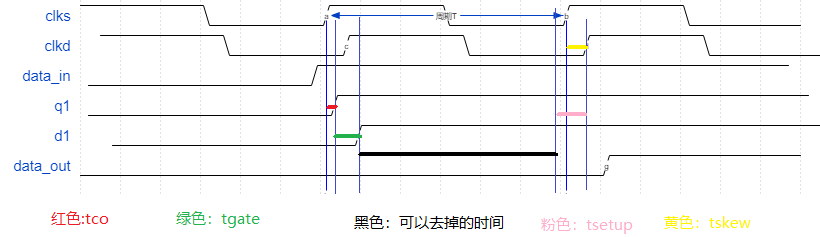

Tclk:时钟周期。两个时钟上升沿之间的时间。

Tco / Tctoq:寄存器更新延迟。clock output delay,时钟触发到数据输出的最大延迟时间。

Tgate / Tdata:逻辑门的延迟。一般包括传播延迟。

Tsetup:触发器的建立时间。

Thold:触发器的保持时间。

Tskew:时钟偏移。同一时钟到达不同的触发器的时钟引脚经历的路径可能存在差异,造成他们的时钟上升沿不是同时出现的,这种偏差称为时钟偏移。通过使用时钟树综合工具可以有效地减少时钟偏移,但是不能消除时钟偏移。

最小时钟周期计算

显然有:T≧tco+tgate+tsetup−tskew

所以最小时钟周期有Tmin=tco+tgate+tsetup−tskew

halftop

即将入行的数字IC设计工程师