verilog99题——5、6、7题

题目

005.十进制转换为二进制编码:127,-127,127.375,-127.375

006.画出CMOS三态缓冲器的电路原理图,解释一下高阻态。

007.什么是open-drain output?

第五题

整数部分最基础的就是“除2取余法”,小数部分是"乘2取整法"。

整数部分比较快捷的方法:127=64+32+16+8+4+2+1=26+25+24+23+22+21+20=(1111111)b。

小数部分没有什么比较快的,就是基础法:0.375×2=0.75取0;0.75×2=1.5取1;0.5×2=1取1。

所以可得

127 → 0111_1111

-127 → 1111_1111

127.375 → 0111_1111.011

-127.375 → 1111_1111.011

第六题

计算机系统的各部件模块(Module)及芯片(Chip)通常挂接在系统总线(System bus)上,在某一时刻只能有一个发送端。为了使各模块芯片能够分时传送信号,需要具有三态输出的门电路,简称三态门(Three-state gate),又称为三态缓冲器(Three-state buffer)三态门的输出端状态不仅有高电平和低电平,而且具有第三种状态--高阻状态(High-Impedance,Hi-Z).

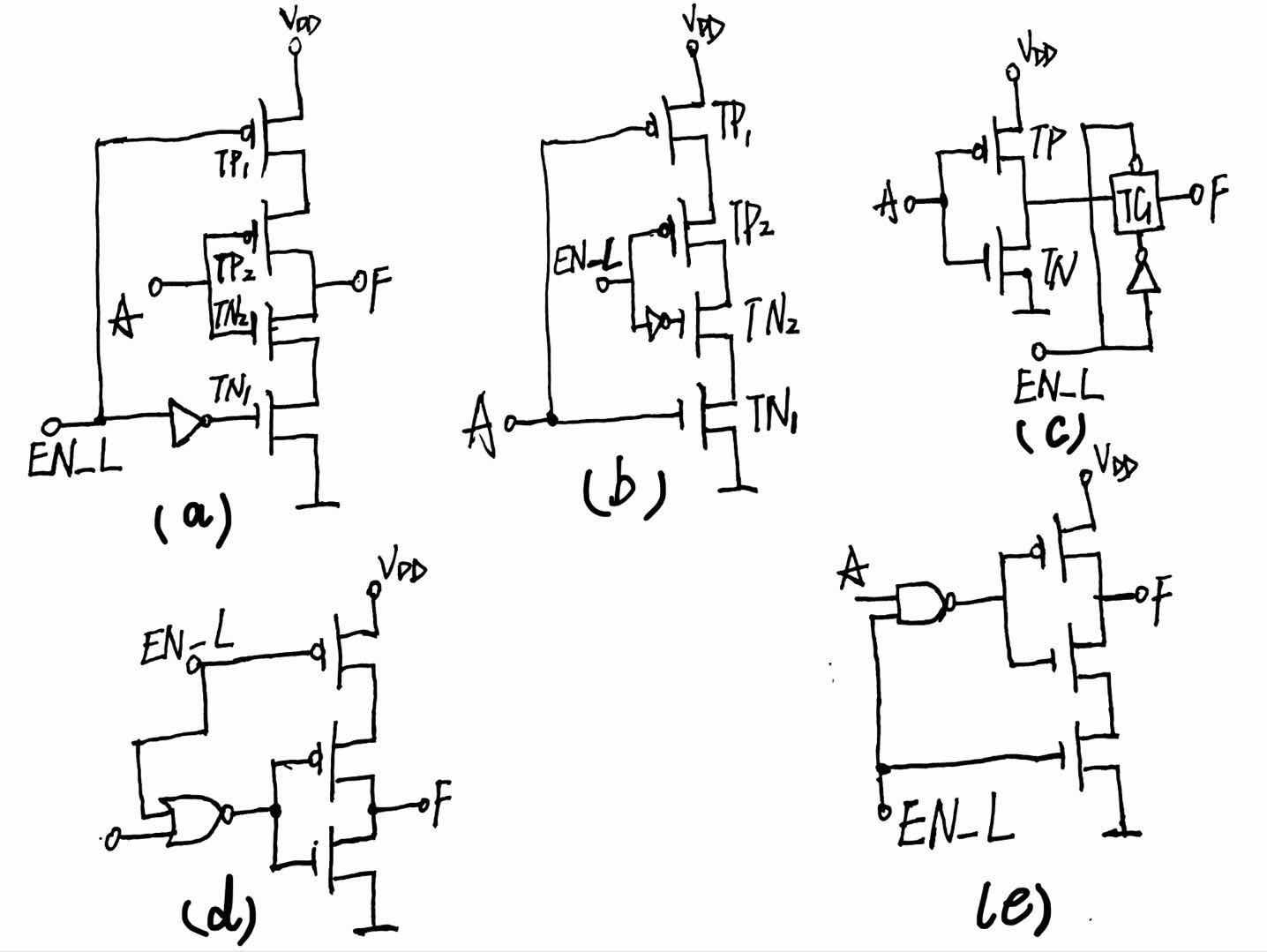

CMOS三态门是在普通门的基础上增加了控制端和控制电路。CMOS三态门的电路结构有很多种,大体可以分为以下3类:

-

控制上下P/N沟道的截止或导通,实现三态输出功能。如下图(a)、(b)。

-

在输出端串联传输门开关(TG)的三态线路。如下图(c)。

-

利用或非门或者与非门实现三态功能。如下图(d)(e)。

第七题

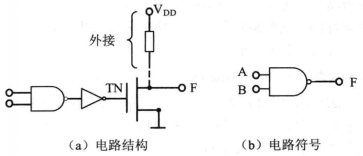

CMOS漏极开路门(Open-Drain Gate),又称漏极开路输出(open-drain output),简称OD门。

各种CMOS门电路都可构成漏极开路门,下图为CMOS与非OD门的电路结构。F=(AB)'

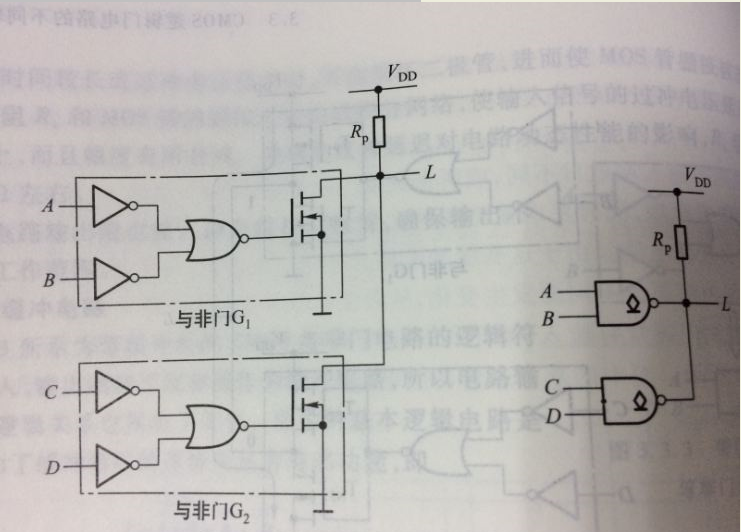

漏极开路OD门电路内的输出MOS管漏极是开路的,应用时,需要通过外接电阻(Extension resistance)接电源。与TTL集成的OC门类似,CMOS集成的OD门也可实现线与(Wired and)连接。

可以看出,OD门就是将反相器的上面的PMOS管拿掉了而已。

当两个与非门的输出全为1时,输出为1;只要其中一个输出为0,则输出为0,所以该电路符合与逻辑功能,即L=(AB)'(CD)'。

即将入行的数字IC设计工程师