verilog99题——1、2题

题目

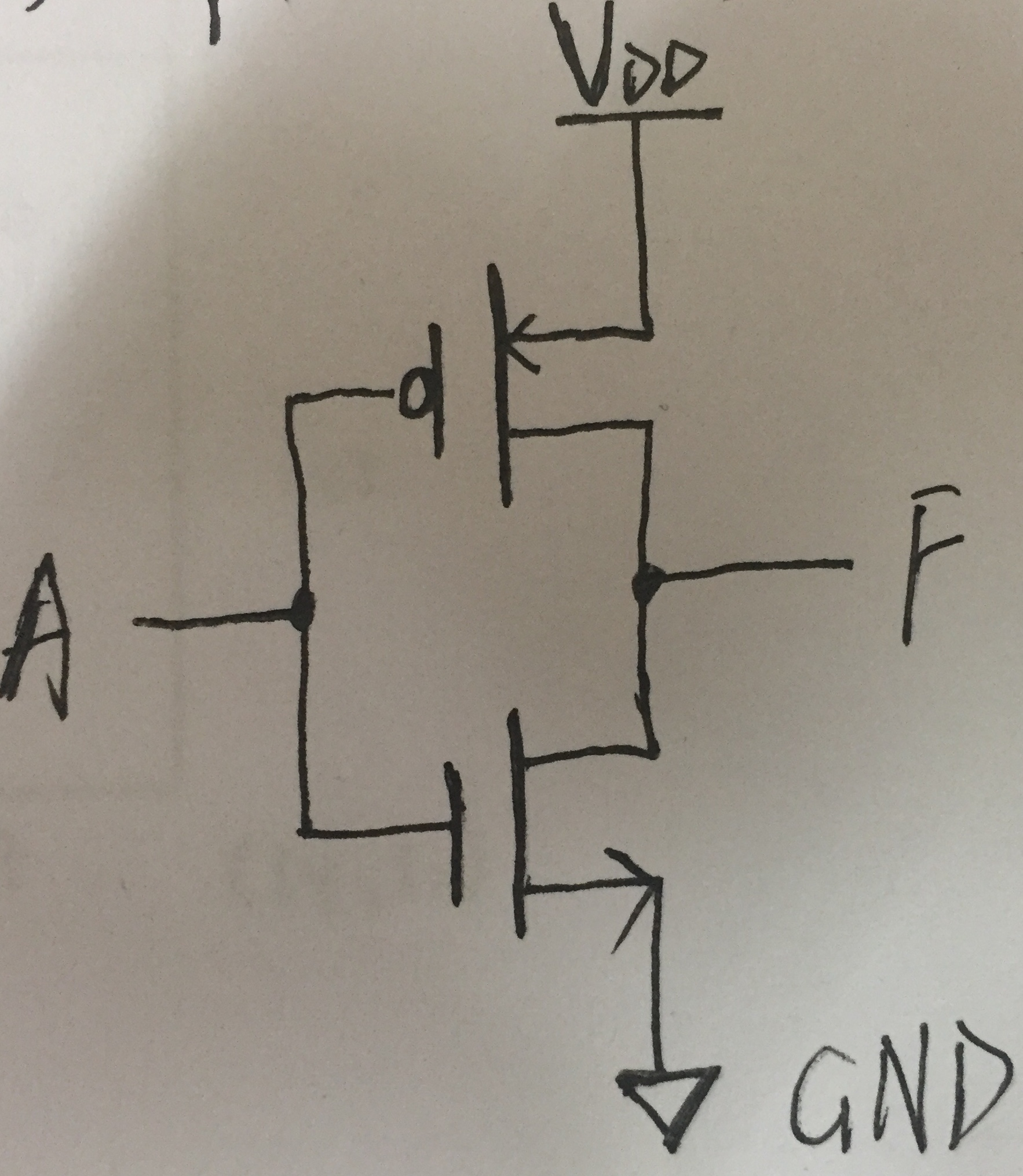

001.画出CMOS反相器的电路原理图。

002.反向器的速度与哪些因素有关?什么是转换时间(transition time)和传播延迟(propagation delay)?

第一题

NMOS——电子导电,高电平通,低电平断,传递低电平→连接地

PMOS——空穴导电,低电平通,高电平断,传递高电平→连接电源

第二题

影响因素:(这个小问只是简单看了一下把答案总结了一下,部分原理没搞懂)

- 电容——门本身的扩散电容,互连线电容(通过版图优化)和扇出电容(尽量减少漏区面积)。

- 增加晶体管的W/L:增加晶体管的尺寸也增加扩散电容。这个有限值,到一定程度,再增加门尺寸就不能对减少延时有帮助了。

- 提高VDD:以能量损耗来换取性能,但电压超过一定程度后改善就会非常有限。

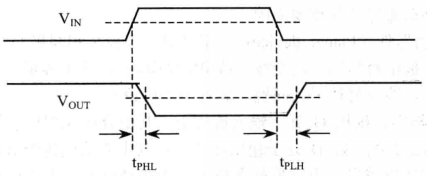

传播延迟(propagation delay):由于PN结上储存电荷的积累和消散都需要时间,因此MOS管由导通到截至或由截止到导通也需要时间。电路中寄生电容和负载电容的影响,也使得输出波形总是滞后于输入波形,这个延迟时间成为传播延迟(propagation delay),或者传输延迟时间。它反映了门电路的开关速度和信号传递时间。

通常,输出信号由低电平变为高电平时,输出相对输入的延迟时间记为tPLH:而输出信号由高电平变为低电平时,输出相对输入的延迟时间记为tPHL。

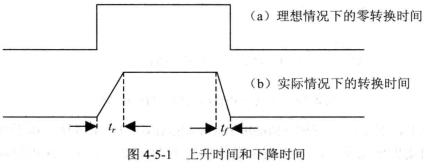

转换时间(transition time):用来描述逻辑电路的输出从一种状态变为另一种状态所需的时间。其中输出从低态到高态的转换时间称为上升时间(tr,rise time);从高态到低态的转换时间称为下降时间(tf,fall time)。

参考文献:姜书艳. 数字逻辑设计及应用[M]. 清华大学出版社, 2014.

halftop

即将入行的数字IC设计工程师